# **Wave Shaping Diode Circuits**

#### Objectives

To understand diode clipping circuits (clipper or limiter)

To understand diode clamping circuits (clamper)

#### **Apparatus**

- Oscilloscope

- Function generator

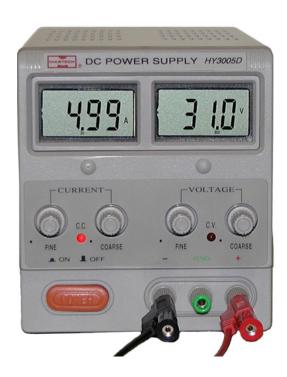

- Bench DC power supplies

- Diode, Resistor, and Capacitor

#### **Basic Information**

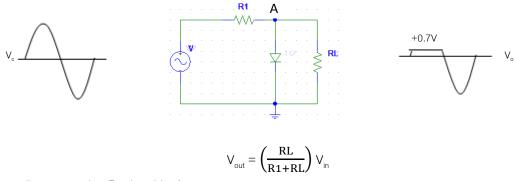

That limits or clips the positive part of the input voltage. As the input voltage goes positive, the diode becomes forward-biased and conducts current. Point A is limited to  $\pm 0.7$  V when the input voltage exceeds this value. When the input voltage goes back below 0.7 V, the diode is reverse-biased and appears as an open. The output voltage looks like the negative part of the input voltage, but with a magnitude determined by the voltage divider formed by  $R_1$  and the load resistor,  $R_1$ , as follows;

If  $R_{l}$  small compared to  $R_{l}$ , then  $V_{out} \cong V_{ln}$

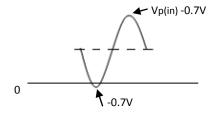

If the diode is turned around, the negative part of the input voltage is clipped off. When the diode is forward-biased during the negative part of the input voltage, point A is held at -0.7V, the diode is no longer forward-biased; and a voltage appears across R<sub>i</sub> proportion to the input voltage.

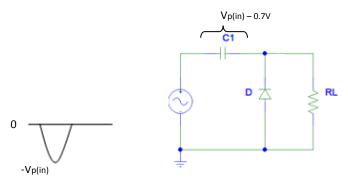

A clamper adds a dc level to an ac voltage. Clampers are sometimes known as dc restores. This figure shows a diode clamper that inserts a positive dc level in the output waveform. The operation of this circuit can be seen by considering the first negative half-cycle of the input voltage. When the input voltage initially goes negative, the diode is forward biased, allowing the capacitor to charge to near the peak of input  $(V_{P(in)}^- 0.7 \text{ V})$ , as show in this figure. Just after the negative peak, the diode is reverse-biased. This is because the cathode is hold near  $V_{P(in)}^- - 0.7 \text{ V}$  by the charge on the capacitor. The capacitor can only discharge through the high resistance of  $R_i$ . So, from the peak of the

one negative half-cycle to the next, the capacitor discharges very little. The amount that is discharged, of cause, depends on the value of  $R_{\rm L}$ .

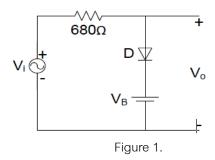

### 1. Clipping circuit I

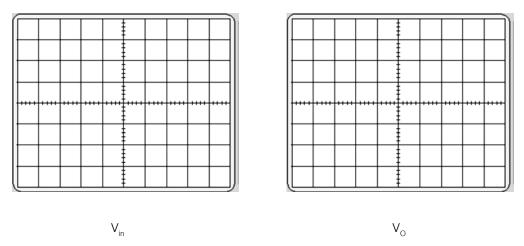

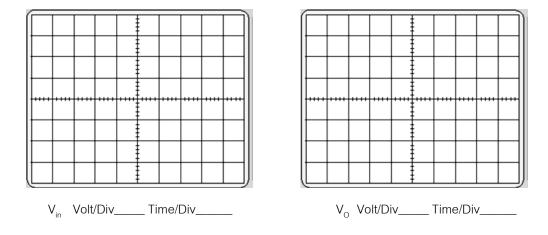

Calculate and plot the output signal  $(V_0)$  as shown in figure 1 compared with the input signal in the same graph. The sinusoidal input  $(V_i)$  has an amplitude of 10  $V_{p,p}$  and frequency of 1KHz. The DC bias voltage  $(V_B)$  is set to 3 volts.

After calculate and plot the output signal  $(V_0)$ . Construct the circuit as shown in figure 1, and set the input signal and the DC bias voltage as in Figure 1. (Use Bench DC power supply to generate this bias voltage. See Appendix.) It is recommended to check the generated voltage with multimeter. This allows more precision when compared with seeing from the supply display. Measure and plot the output signal compared with the input signal in the same graph.

Reverse the direction of diode in figure 1, and set the input signal and the DC bias voltage as in figure 1. Measure and plot the output signal compared with the input signal in the same graph.

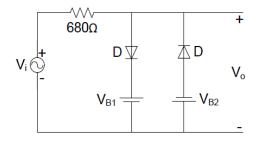

# 2. Clipping circuit II

Calculate and plot the output signal  $(V_0)$  as shown in figure 2 compared with the input signal in the same graph. The sinusoidal input  $(V_i)$  has an amplitude of 10  $V_{P,P}$  and frequency of 1KHz. The DC bias voltage VB1 and VB2 are set to 3 volts and 1 volt, respectively.

Figure 2

After calculate and plot the output signal  $(V_0)$ . Construct the circuit as shown in figure 1, and set the input signal and the DC bias voltage as in Figure 1. Measure and plot the output signal compared with the input signal in the same graph.

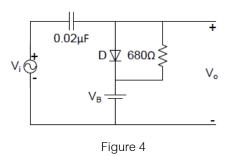

#### Clamping circuit I

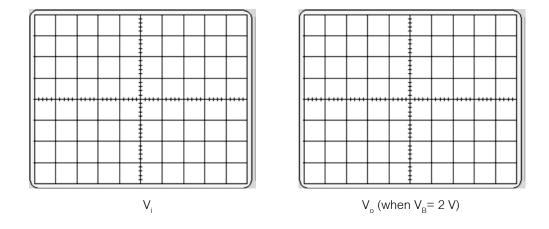

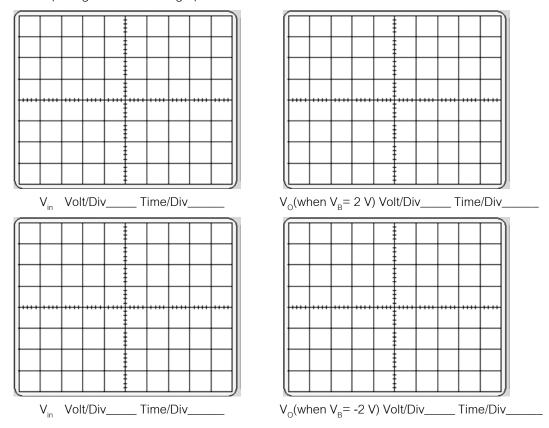

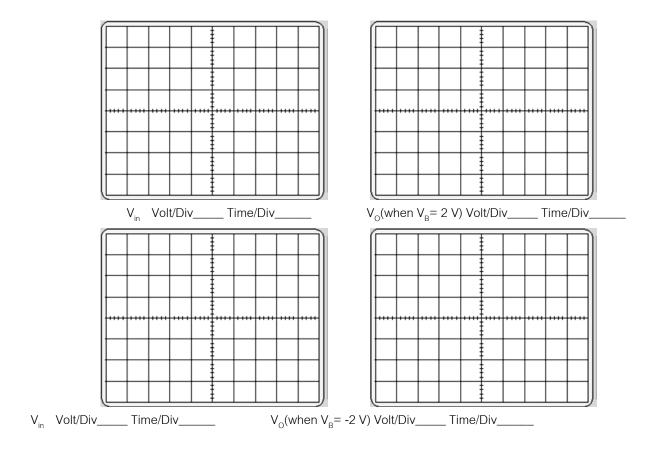

Calculate and plot the output signal  $(V_0)$  as shown in figure 4 compared with the input signal in the same graph. The sinusoidal input  $(V_i)$  has an amplitude of  $10V_{P-P}$  and frequency of 1KHz. The DC bias voltage  $V_B$  is Set DC bias voltage  $V_B$  to 2 volt and -2 volt.

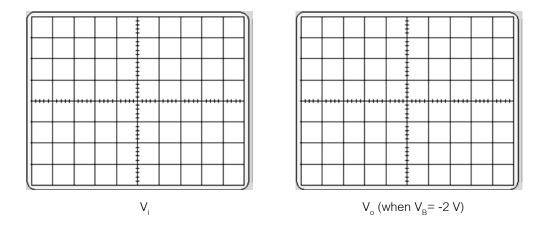

Construct the circuit as shown in figure 4. The sinusoidal input  $(V_i)$  has an amplitude of  $10V_{p,p}$  and frequency of 1KHz. The DC bias voltage  $V_B$  is Set DC bias voltage  $V_B$  to 2 volt and -2 volt. Measure and plot the output signal compared with the input signal in the same graph.

Reverse the direction of diode in figure 4, and set the input signal and the DC bias voltage as in figure 4. Measure and plot the output signal compared with the input signal in the same graph.

# Question I

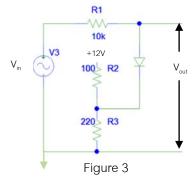

Calculate and plot the output signal ( $V_0$ ) as shown in figure 3. The sinusoidal input ( $V_i$ ) has an amplitude of 10  $V_{p,p}$  and frequency of 1KHz.

|        |        |     |          |   |     |               | =             |               |               |               |

|--------|--------|-----|----------|---|-----|---------------|---------------|---------------|---------------|---------------|

|        | 11     |     |          |   |     | -             |               |               |               |               |

|        | 11     |     |          |   | 1 1 | + 1           |               |               | - 1           | - 1           |

|        | 11     |     |          |   | 1 3 |               |               |               | - 1           | - 1           |

|        | !      | -   | -        |   | -   | $\overline{}$ | -             | $\rightarrow$ | $\rightarrow$ | $\overline{}$ |

|        | 11     |     |          |   |     | t I           |               |               | - 1           | - 1           |

|        | 11     |     |          |   | 1 1 | 1 1           |               |               | - 1           | - 1           |

|        | 11     | I . |          |   |     |               |               |               | - 1           | - 1           |

|        | 11     | _   | -        | - |     |               |               | $\overline{}$ | $\overline{}$ | $\neg$        |

|        | 11     | I . |          |   |     | [ ]           |               |               | - 1           | - 1           |

|        | 11     |     |          |   |     |               |               |               | - 1           | - 1           |

|        | 11     |     |          |   | 1 1 | •             |               |               | - 1           | - 1           |

|        |        |     |          |   |     |               |               |               | $\neg$        | $\neg$        |

| •••••• | 11     | I . |          |   |     | -             |               |               | - 1           | - 1           |

|        | 11     |     |          |   | 1 1 | t I           |               |               | - 1           | - 1           |

|        | 11     |     |          |   |     |               |               |               |               |               |

|        | 11     |     |          |   |     |               |               |               |               |               |

|        | 11     |     |          |   | 1 1 | t I           |               |               | - 1           | - 1           |

|        | 11     | I . |          |   |     |               |               |               | - 1           | - 1           |

|        | 11     | _   | -        |   | -   | -             |               | $\overline{}$ | $\rightarrow$ | $\neg$        |

|        | 11     |     |          |   | 1 1 |               |               |               | - 1           | - 1           |

|        | 11     | I . |          |   |     | -             |               |               | - 1           | - 1           |

|        | 11     |     |          |   |     |               |               |               |               |               |

|        |        |     |          |   |     |               |               |               | -             | $\neg$        |

|        | 11     | I . |          |   |     |               |               |               | - 1           | - 1           |

|        | 11     | I   | i 1      |   | 1 1 | 1             |               |               | - 1           | - 1           |

|        |        | -   | $\vdash$ |   | _   | _             | $\overline{}$ | $\rightarrow$ | $\rightarrow$ | $\overline{}$ |

|        | 11     | I   | i 1      |   |     | t l           |               | <b> </b>      | - 1           | - 1           |

|        | 11     | I   | i 1      |   | 1 1 | 1             |               |               | - 1           | - 1           |

|        | u      | I . |          |   |     |               |               |               | - 1           | - 1           |

|        | $\sim$ |     |          |   |     |               |               | $\overline{}$ | _             | -             |

## Appendix( How to use DC power supply)

- . There are 3 output terminals, Red (+), Black(-) and Green. Basically, the output voltage is taken from Red and Black terminals.

- The output voltage can be adjusted using both fine and coarse knob.

- The current setting is used to limit maximum current generated by the supply. If a red LED is shown, this means the current drawn from the supply is exceed the maximum limit. To solve this problem, increase the maximum current using both knobs