# **Transistor Configuration**

#### Objectives

- To review BJT biasing circuit.

- To study BJT amplifier circuit

- To understand the BJT configuration.

- To analyse single-stage BJT amplifier circuits.

- To study the differential amplifier.

- To design amplifier circuits.

#### **Transistor Biasing Circuits**

- Voltage Divider Bias

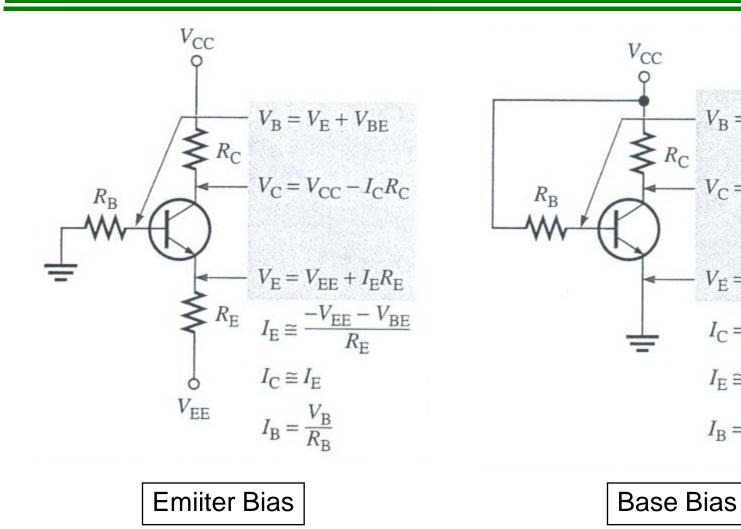

- Emitter Bias

- Base Bias

- Emitter-feedback Bias

- Collector-feedback Bias

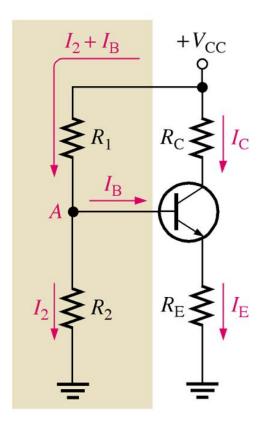

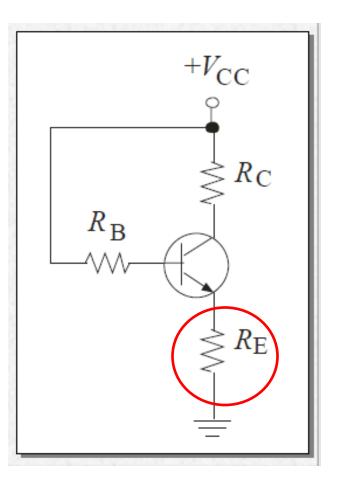

## Voltage Divider Bias

Voltage-divider bias is the most widely used type of bias circuit. Only one power supply is needed and voltage-divider bias is more stable( $\beta$  independent) than other bias types. For this reason it will be the primary focus for study.

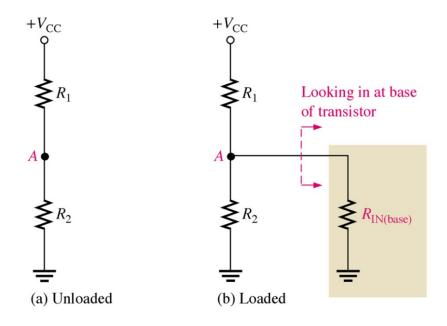

In the case where base to ground resistance(input resistance) is low enough to consider, we can determine it by the simplified equation  $R_{IN(base)} = \beta_{DC}R_{E}$

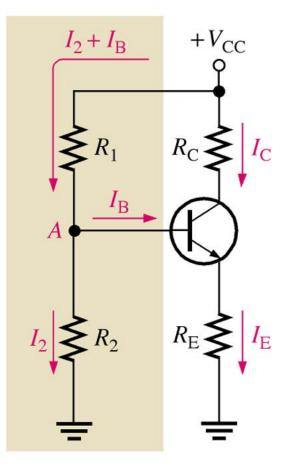

We can view the voltage at point A of the circuit in two ways, with or without the input resistance(point A to ground) considered.

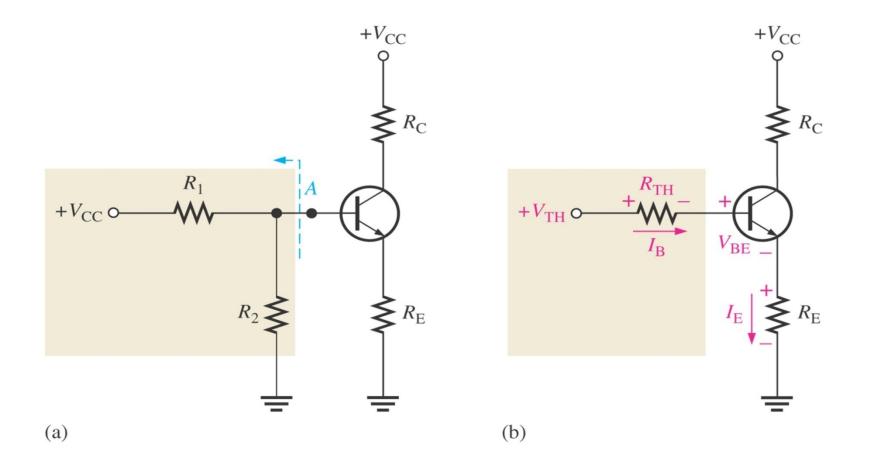

### Thevinizing the bias circuit

## Stiff voltage divider

Stiff voltage divider: (No loading effect)

- 1.  $I_B$  is much smaller than  $I_2$

- **2.**  $R_{IN(BASE)} = \beta_{DC} R_E > 10 R_2$

$V_{\rm B} = (R_2/(R_1 + R_2))V_{\rm CC}$  $I_{\rm E} \approx I_{\rm C}$

Non-Stiff voltage divider: (with loading effect)

$$\mathbf{V}_{\mathrm{B}} = \left(\frac{\mathbf{R}_{2} \parallel \beta_{DC} \mathbf{R}_{E}}{\mathbf{R}_{1} + (\mathbf{R}_{2} \parallel \beta_{DC} \mathbf{R}_{E})}\right) \mathbf{V}_{CC}$$

$+V_{\rm CC}$

$V_{\mathrm{BE}}$  .

$R_{C}$

$\beta_{DC}$

$+V_{\rm CC}$

$I_2 + I_B$

$R_2$

We now take the known base voltage and subtract  $V_{BF}$  to find out what is dropped across  $R_{F}$ . Knowing the voltage across  $R_{F}$ we can apply Ohm's law to determine the current in the collector-emitter side of the circuit. Remember the current in the base-emitter circuit is much smaller, so much in fact we can for all practical purposes we say that  $I_{F}$  approximately equals  $I_{C}$ .

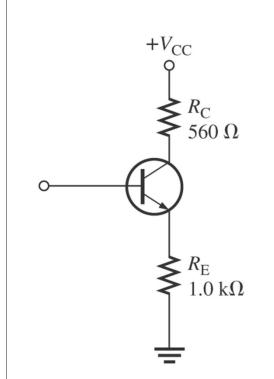

• Determine the dc input resistance looking at the base of the transistor if  $\beta_{DC} = 125$ .

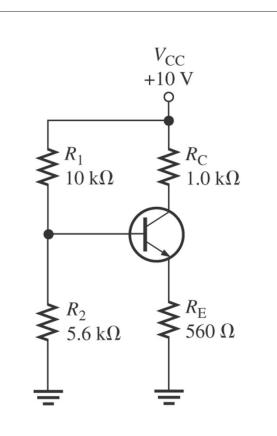

• Determine  $V_{CE}$  and  $I_{C}$  in the stiff voltage divider biased transistor circuit if  $\beta_{DC} = 100$ .

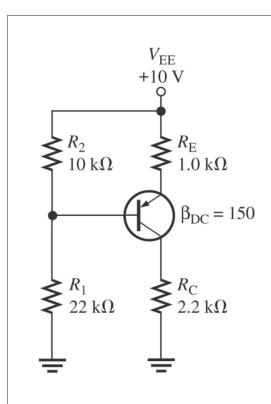

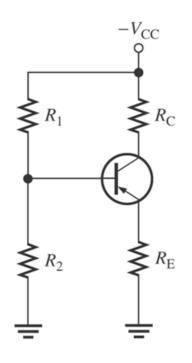

• Find  $I_C$  and  $V_{EC}$  for the pnp transistor circuit as given.

• Find I<sub>C</sub> and V<sub>CE</sub> for the pnp transistor circuit as given. Assume R<sub>1</sub>=68 k $\Omega$ , R2= 47 k $\Omega$ , R<sub>C</sub>= 1.8 k $\Omega$ , R<sub>E</sub>= 2.2 k $\Omega$ , V<sub>CC</sub>= -6 V and  $\beta$  <sub>DC</sub> = 75.

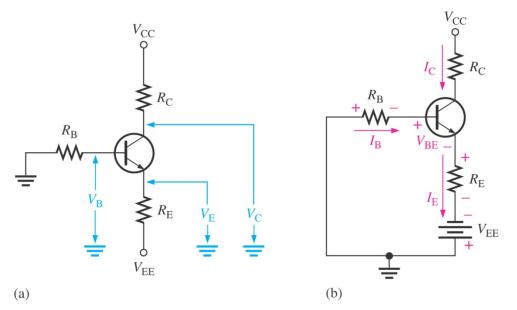

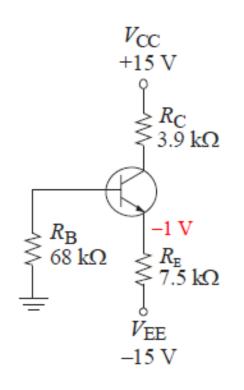

## **Emitter Bias**

This type of circuit is independent of  $\beta$  making it as **stable** as the voltage-divider type. The drawback is that it requires two power supplies.

Two key equations for analysis of this type of bias circuit are shown below. With these two currents known we can apply Ohm's law and Kirchhoff's law to solve for the voltages.

Approximation calculation:

V<sub>E</sub> = V<sub>B</sub>-V<sub>BE</sub> ≈ -1 V V<sub>E</sub> = I<sub>E</sub>R<sub>E</sub> + V<sub>EE</sub> I<sub>C</sub> ≈ I<sub>E</sub> = (-V<sub>EE</sub>- 1)/R<sub>E</sub> independent of β

Precise calculation:

$I_{B} \approx I_{E} / \beta$  $I_{C} \approx I_{E} \approx (-V_{EE} - V_{BE}) / (R_{E} + R_{B} / \beta_{DC})$

• Assuming that  $V_E = -1 V$ , what is  $I_E$ ?

This type of circuit is very unstable since its  $\beta$  changes with temperature and collector current. Base biasing circuits are rarely used in linear circuits and mainly limited to switching applications.

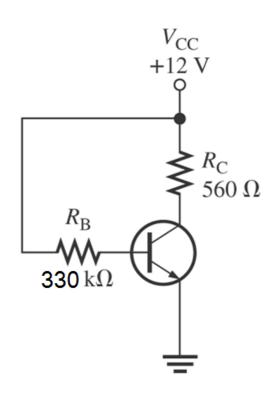

**Base Bias**

KVL around base and collector circuits;

$-V_{CC}+I_{B}R_{B}+V_{BE}=0$   $I_{B} = (V_{CC}-V_{BE})/R_{B}$   $I_{C} = \beta_{DC} I_{B}$   $I_{C} = \beta_{DC} (V_{CC}-V_{BE})/R_{B}$   $\uparrow$ dependent of  $\beta$

$$V_{CE} = V_{CC} - I$$

Ko

• Determine how much Q-point( $I_C$  and  $V_{CE}$ ) for the given circuit will change a over temperature range where  $\beta_{DC}$  increases from 100 to 200.

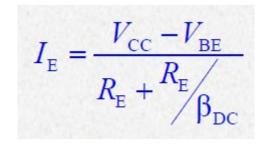

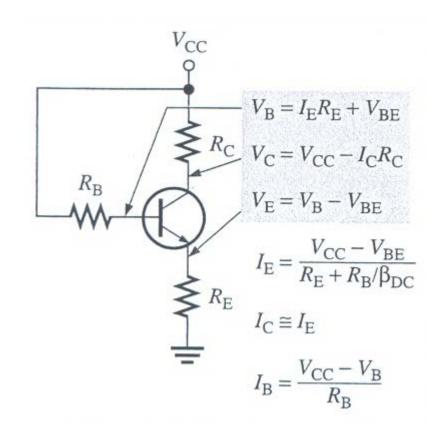

### Emitter-feedback bias

R<sub>E</sub> changes base bias into emitterfeedback bias, which is **more predictable**. This is a form of negative feedback.

KVL around base circuit;

$-V_{CC}+I_{B}R_{B}+V_{BE}+I_{E}R_{E}=0$

$\textbf{I}_{\text{E}}/\beta_{\text{DC}}{=}\textbf{I}_{\text{B}}$

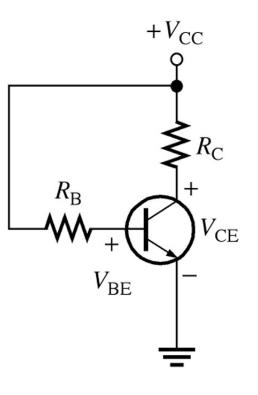

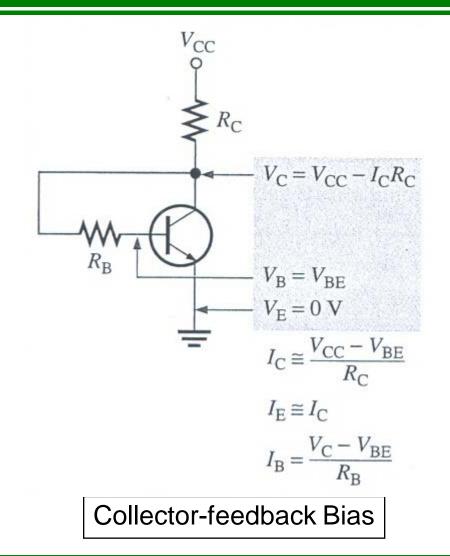

### Collector-feedback bias

Collector-feedback bias is kept stable with negative **feedback**, although it is not as stable as voltage-divider or emitter bias. With increases of  $I_{C,}$  less voltage is applied to the base. With less  $I_{B,}I_{C}$  comes down as well. The two key formulas are shown below.

$|I_{C} + I_{B}| \neq R_{C}$   $R_{B}$   $V_{C}$   $I_{C}$   $I_{C}$   $V_{C}$   $I_{C}$   $I_{C}$   $I_{C}$   $I_{C}$   $I_{C}$   $I_{C}$   $I_{C}$   $I_{C}$

$$I_{\rm B} = V_{\rm C} - V_{\rm BE}/R_{\rm B}$$

$$I_{\rm C} = V_{\rm CC} - V_{\rm BE}/R_{\rm C} + R_{\rm B}/\beta_{\rm DC}$$

## Review Summary(1)

$\succ$  The purpose of biasing is to establish a stable operating point (Q-point).

> The Q-point is the best point for operation of a transistor for a given collector current.

> The dc load line helps to establish the Q-point for a given collector current.

$\succ$  The linear region of a transistor is the region of operation within saturation and cutoff.

## Review Summary (2)

> Voltage-divider bias is most widely used because it is stable and uses only one voltage supply.

- > Base bias is very unstable because it is  $\beta$  dependent.

- Emitter bias is stable but require two voltage supplies.

> Collector-feedback is relatively stable when compared to base bias, but not as stable as voltage-divider bias.

#### Summary of Bias Circuits(1)

#### Summary of Bias Circuits(2)

$V_{\rm B} = V_{\rm BE}$

$V_{\rm E} = 0 \, {\rm V}$

$I_{\rm E} \cong I_{\rm C}$

$I_{\rm B} = \frac{V_{\rm CC} - V_{\rm BE}}{R_{\rm P}}$

$-V_{\rm C} = V_{\rm CC} - I_{\rm C} R_{\rm C}$

$I_{\rm C} = \beta_{\rm DC} \left( \frac{V_{\rm CC} - V_{\rm BB}}{R_{\rm P}} \right)$

#### Summary of Bias Circuits(3)

**Emitter-feedback Bias**

## Supplement

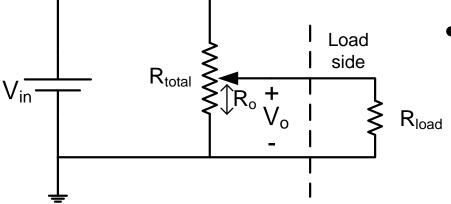

## Loading Effect

The load resistance connected to the potentiometer introduce the error to the output voltage

• [Unloaded] Without R<sub>load</sub>,

$$V_o = \frac{R_o}{R_{total}} V_{in}$$

• [Load] With R<sub>load</sub>,

$$V_o = \frac{R_o //R_{load}}{(R_{total} - R_o) + R_o //R_{load}} V_{in}$$

- Loading Error:

- $V_o[unloaded] V_o[load]$

#### Exercise

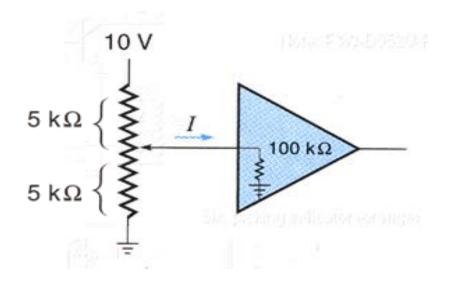

From a given circuit, the output voltage from the potentiometer is used to drive the load with 100kΩ resistance. As a result, the loading error is applied at the output of the pot. What is the value of loading error in volts??? Explain the method to overcome this problem??

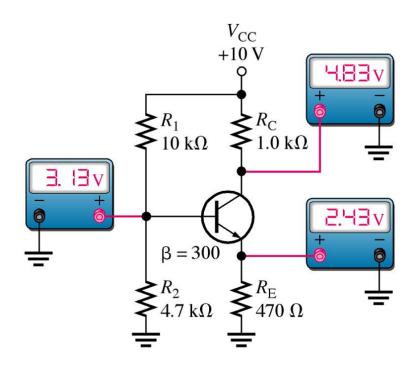

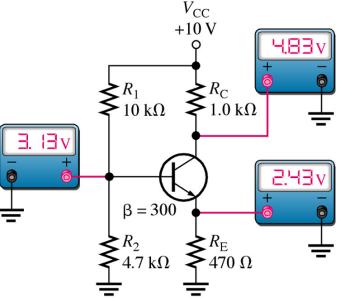

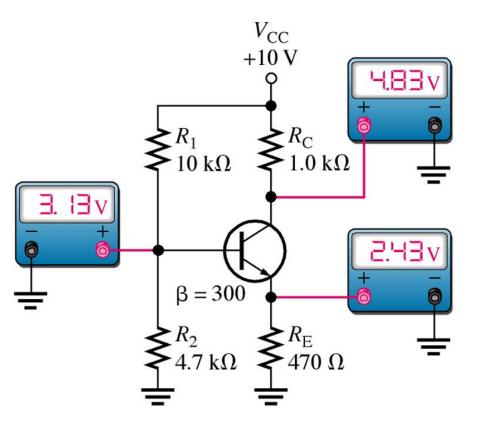

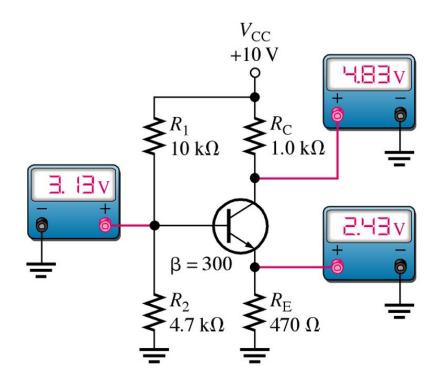

## Troubleshooting

Shown is a typical voltage divider circuit with correct voltage readings. Knowing these voltages is a requirement before logical troubleshooting can be applied. We will discuss some of the faults and symptoms.

#### R1 Open

With no bias the transistor is in cutoff.

Base voltage goes down to 0 V.

Collector voltage goes up to 10  $V(V_{CC})$ .

Emitter voltage goes down to 0 V.

#### **Resistor** R<sub>E</sub> Open:

Transistor is in cutoff.

Base reading voltage will stay approximately the same.

Collector voltage goes up to  $10 V(V_{CC})$ .

Emitter voltage will be approximately the base voltage + .7 V.

#### **Base Open Internally:**

Transistor is in cutoff.

Base voltage stays approximately the same.

Collector voltage goes up to 10 V( $V_{CC}$ ).

Emitter voltage goes down to 0 V.